Exceptional level is a logical separation of software execution privilege, similar to ring in x86.

1. ARMv8-A特权级

ARMv8-A中特权级(privilege level)的概念被称为异常级别(EL, exception level),它是程序运行所处特权级别的逻辑划分。异常级别被划分为以下四种,注意到数字越大,特权越高:

- EL0:通常用户程序

- EL1:操作系统内核

- EL2:虚拟机监视器

- EL3:低级固件,包括Secure Monitor

通常情况下,一个软件,例如应用程序,操作系统内核或是虚拟机监视器仅占据一个异常级别。一个例外是in-kernel监视器例如KVM,它跨越了EL2和EL1。

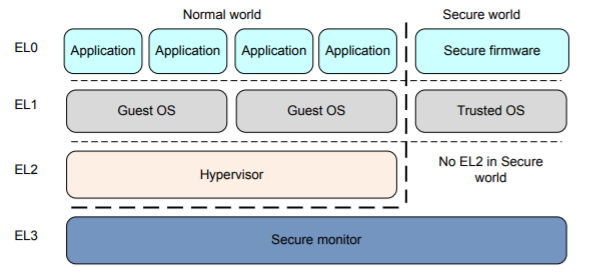

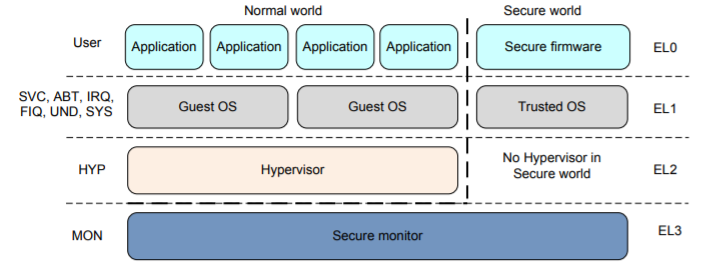

ARMv8-A提供了两个安全状态(Security states)。Non-secure state被称为Normal world,secure state被称为Secure World。

操作系统运行在Normal world中,和它并行地有一个trusted OS运行在Secure World。ARM TrustZone技术让系统能够划分为Normal和Secure world部分。这种划分为某些软件/硬件攻击提供了保护。Secure monitor在其中扮演了Normal和Secure world间gateway的角色,其特权级最高。

ARMv8-A也为虚拟化提供了硬件支持。这意味着虚拟机监视器/VMM能够在系统中运行,并支持多个客户OS。

如上图。Normal World中有以下组件:

- 应用程序

- 客户操作系统

- 虚拟机监视器

Secure World中有以下组件

- secure固件:它必须是boot time运行的第一个程序,提供平台初始化、trusted OS安装、Secure monitor调用的路由。运行在EL3。

- trusted os:Trusted OS为Normal World提供安全服务并为执行Secure或trusted的应用程序提供运行时环境。当EL3使用AArch64时,它在Secure EL1执行,当EL3使用AArch32时,它在Secure EL3执行。

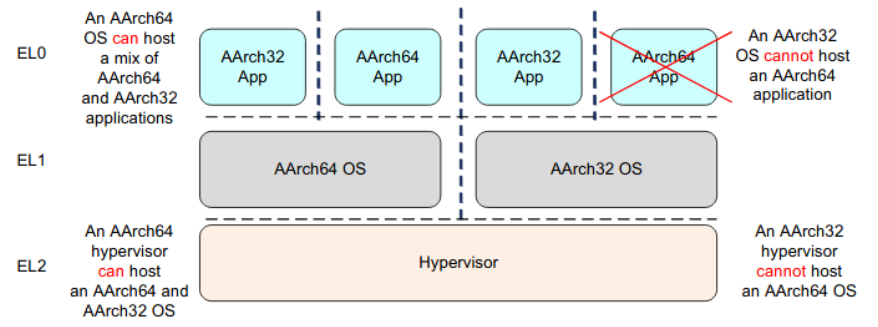

2. 执行状态(Execution states)

ARMv8-A架构定义了AArch64(有时称为ARM64)和AArc32两个执行状态(both unique to overall ARMv8-A)。AArch64状态仅纯在于ARMv8-A中,使用64位通用寄存器。AArch32向后和使用32位通用寄存器的ARMv7-A兼容。

3. 异常级别切换

对于每一种异常类型,架构定义了处理异常的模式。该模式被称为异常对应的target mode。

ARMv8-A AArch32遵循以下模型,当处理器接收到异常(例如中断和系统调用):

- 将当前处理器状态保存在target mode的SPSR中

- 为异常保存返回地址

- 若target mode非Hyp mode,保存在target mode的Link Register(LR)中

- 否则,保存在ELR_hyp中

- 移动到target mode。除非target mode是Monitor mode,这种移动不修改Security state。

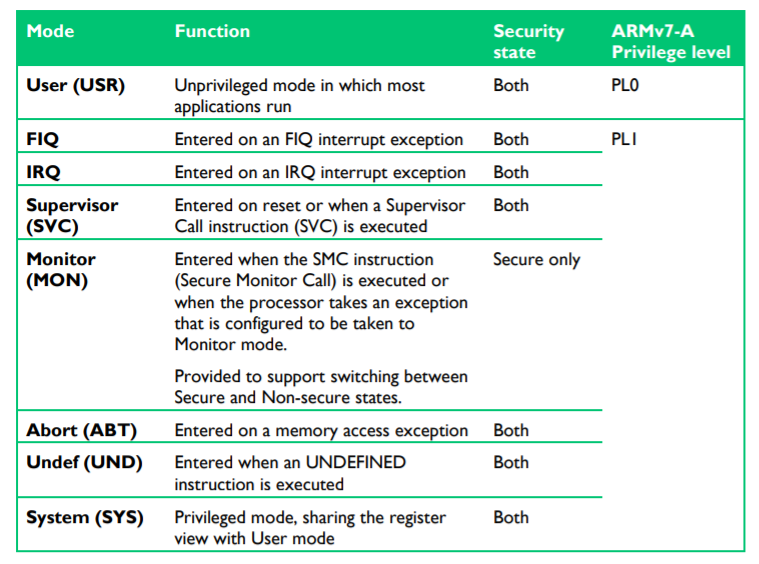

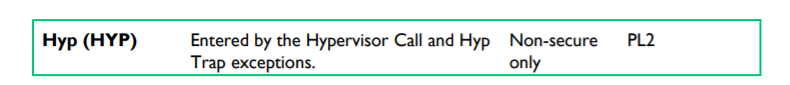

ARMv7-A架构使用PL0到PL2的特权级。ARMv8-A中,异常级别取代了特权级。下表展示了(包括了虚拟化扩展和安全扩展的)ARMv7-A的所有处理器模式和对应的执行特权级。执行特权级和security mode是独立定义的。

ARMv7-A架构中,处理器模式能够在特权软件控制或处理异常时自动切换。当异常发生,处理器核保存当前执行状态核返回地址,进入处理异常的模式,同时可能禁止中断。

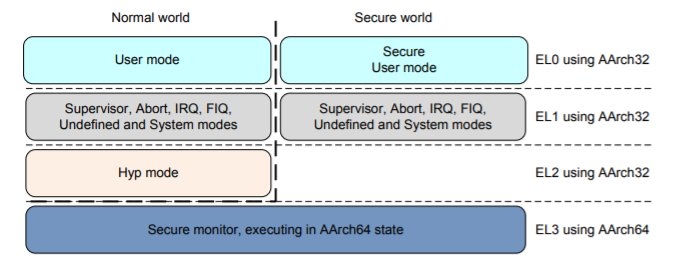

如上图应用程序运行在最低特权级PL0。OS运行在PL1,hypervisor运行在PL2。Secure monitor也允许在PL1。

ARMv8-A没有改变上述异常模型,但是增加了下面的规则:

- 若EL2使用AArch64,则任何目标为Hyp mode 的异常在EL2使用AArch64处理

- 若EL3使用AArch64,则任何目标为Monitor mode 的异常在EL3使用AArch64处理

在AArch64,处理器模式和异常级别的映射如下

注意到,AArch32中Secure monitor运行在PL1,而AArch64中其在EL3运行。

3.1. 映射处理器模式到异常级别

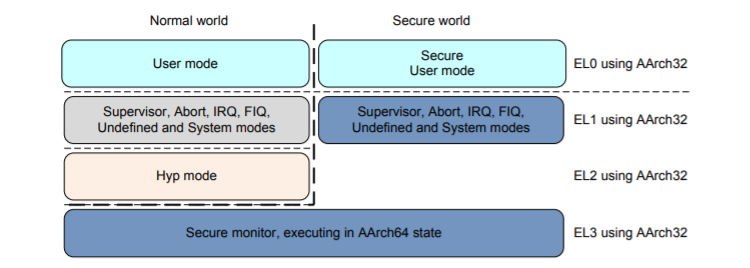

Secure state中的异常级别取决于EL3是否使用AArch64。这影响了处理器模式和异常级别的映射关系。

当EL3使用AArch64时:

因为EL3提供了Secure Monitor的功能且EL3使用AArch64,ARMv8-A中没有ARMv7-A的monitor mode。

当EL3使用AArch32时:

从这两个图,Normal World的映射没有变化,但是Secure world中Supervisor mode,abort mode,IRQ mode,FIQ mode,Undefined mode和System mode从EL1晋升到了EL3,这因为

- EL3提供了Secure monitor的功能

- ARMv6安全扩展将monitor mode以及上述mode定义为Secure state mode。因此这些模式都映射到EL3作为Secure Monitor的功能。

这种重映射对处理器操作没有影响。AArch32状态的变化仅定义为处理器模式

3.2. ARMv8-A的特权级

当EL3使用AArch32时(Supervisor mode,abort mode,IRQ mode,FIQ mode,Undefined mode和System mode)在Secure state中是EL3 modes,否则总是EL1 modes。

3.3. 执行状态与寄存器

每一个处理器核的执行状态表示为:

- 寄存器文件

- 处理器状态(PSTATE)

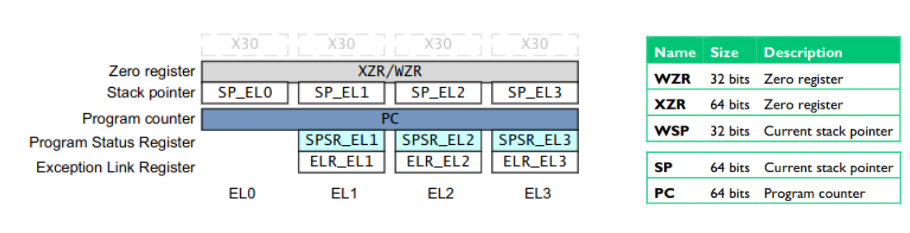

3.3.1. AArch64的寄存器

通用寄存器:

- 31个64位通用寄存器(X0-X30)

- 64位宽:Xn

- 32位宽:Wn

- 64/32位宽:Rn

1 | |

专用寄存器:

- XZR(非X0): zero register

- SP/PC: 栈和程序计数器

- SPSR: saved program status 保存程序状态

- ELR: exception link register

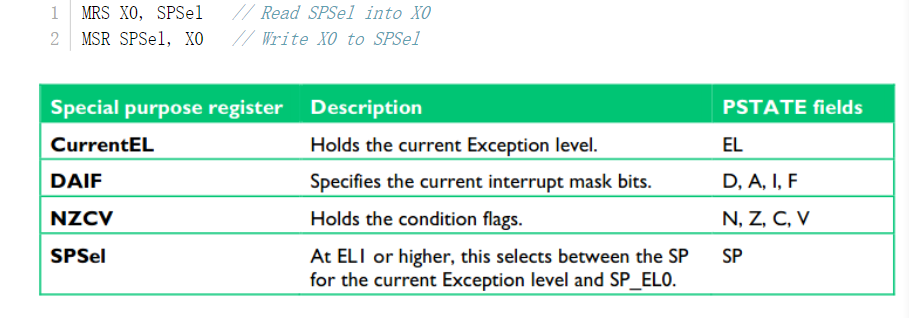

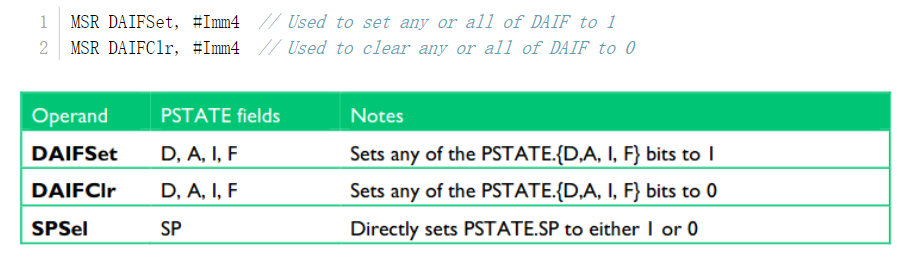

3.3.2. 处理器状态(PSTATE)

- Conditional flags: N, Z, C, V

- Interrupt masks: D, A, I, F

- Execution state: nRW (32/64-bit)

- Stack selection: SP (SP_EL0/SP_ELn)

- Misc: SS (single step), IL (illegal execution)

访问PSTATE的方式如下

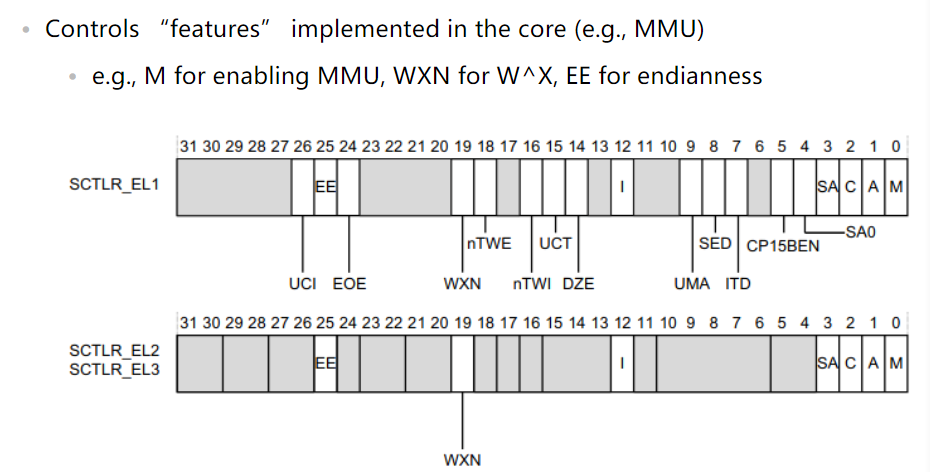

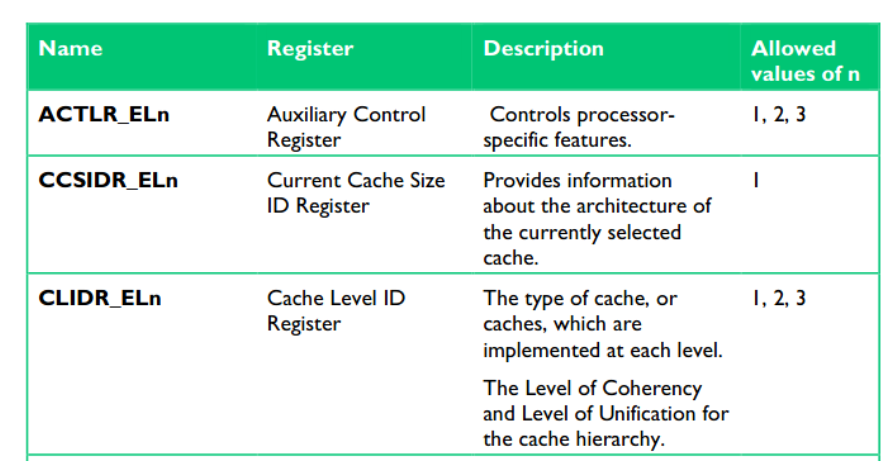

3.3.3. 系统寄存器

3.3.4. 系统控制寄存器